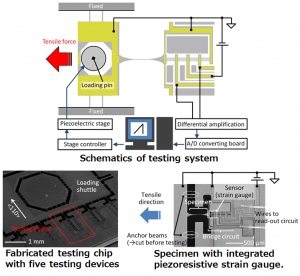

In order to shorten a testing time for evaluation of tensile-mode fatigue properties of single crystal silicon, we have developed parallelized tensile-testing method with an integrated strain gauge. The testing method increases a loading frequency to higher than 100 Hz because of a high stiffness of testing system, and shortens a testing time per one specimen due to the parallelization. The integrated strain gauge is based on a piezoresistive effect of single crystal silicon. Low-noise output is acquired from an integrated bridge circuit on a testing chip.

In order to shorten a testing time for evaluation of tensile-mode fatigue properties of single crystal silicon, we have developed parallelized tensile-testing method with an integrated strain gauge. The testing method increases a loading frequency to higher than 100 Hz because of a high stiffness of testing system, and shortens a testing time per one specimen due to the parallelization. The integrated strain gauge is based on a piezoresistive effect of single crystal silicon. Low-noise output is acquired from an integrated bridge circuit on a testing chip.

[Applications]

- Database of fracture strength of single crystal silicon

- Design guideline of MEMS devices with higher reliability

[Publications]

- A. Uesugi, Y. Hirai, T. Tsuchiya, O. Tabarta, “Parallel Tensile-Mode Fatigue Testing of Silicon Microstructures with Integrated Piezoresistive Stain Sensors”, 28th International Microprocesses and Nanotechnology Conference (MNC 2015), November 2015.